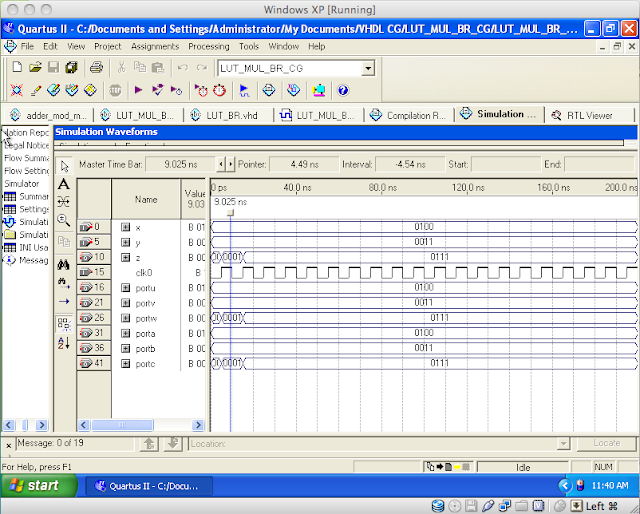

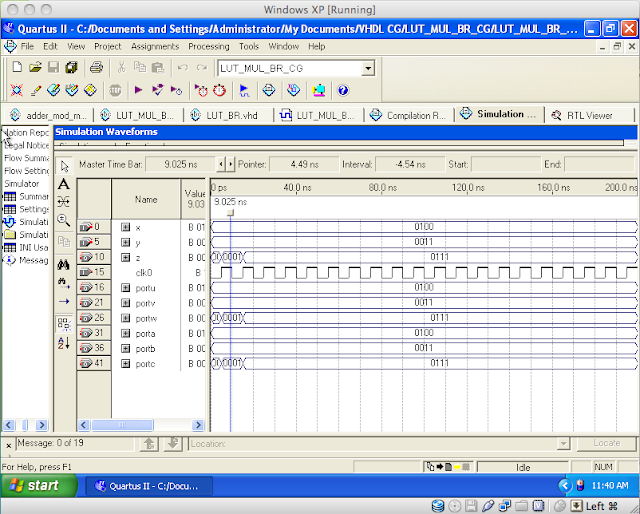

LUT_MUL_BR_CG.vhdl

library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity LUT_MUL_BR_CG is

port (

clk0 : in std_logic;

x, y: in std_logic_vector(3 downto 0);

z: out std_logic_vector(3 downto 0);

portu, portv, portw: out std_logic_vector(3 downto 0);

porta, portb, portc: out std_logic_vector(3 downto 0)

);

end LUT_MUL_BR_CG;

architecture rtl of LUT_MUL_BR_CG is

component LUT_BR

port (

clk : in std_logic;

a, b: in std_logic_vector(3 downto 0);

c: out std_logic_vector(3 downto 0);

porta, portb, portc: out std_logic_vector(3 downto 0)

);

end component;

signal u : std_logic_vector(3 downto 0);

signal v : std_logic_vector(3 downto 0);

signal w : std_logic_vector(3 downto 0);

begin

u <= x;

v <= y;

lutmul: lut_br port map(clk0, u, v, w, porta, portb, portc);

z <= w;

portu <= u;

portv <= v;

portw <= w; end rtl;

LUT_BR.vhdl

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity LUT_BR is

port (

clk: in std_logic;

a, b: in std_logic_vector(3 downto 0);

c: buffer std_logic_vector(3 downto 0);

porta, portb, portk, portc: out std_logic_vector(3 downto 0)

);

end entity LUT_BR;

architecture behavioral of LUT_BR is

component adder_mod_m_CG

port (

x, y: in std_logic_vector(3 downto 0);

addb_sub: in std_logic;

z: buffer std_logic_vector(3 downto 0)

);

end component;

signal z : std_logic := ‘0’;

signal i : std_logic_vector(3 downto 0);

signal j : std_logic_vector(3 downto 0);

signal k : std_logic_vector(3 downto 0);

begin

process(clk)

begin

if clk’event and clk = ‘1’ then

case a is

when "0001" => i <= "0000";

when "0010" => i <= "0001";

when "0011" => i <= "0011";

when "0100" => i <= "0010";

when "0101" => i <= "0110";

when "0110" => i <= "0100";

when "0111" => i <= "0101";

when others => i <= "0000";

end case;

case b is

when "0001" => j <= "0000";

when "0010" => j <= "0001";

when "0011" => j <= "0011";

when "0100" => j <= "0010";

when "0101" => j <= "0110";

when "0110" => j <= "0100";

when "0111" => j <= "0101";

when others => j <= "0000";

end case;

case k is

when "0000" => c <= "0001";

when "0001" => c <= "0010";

when "0010" => c <= "0100";

when "0011" => c <= "0011";

when "0100" => c <= "0110";

when "0101" => c <= "0111";

when "0110" => c <= "0101";

when others => c <= "0000";

end case;

end if;

end process;

porta <= a;

portb <= b;

portk <= k;

portc <= c;

adderku: adder_mod_m_CG port map (i, j, z, k);

end architecture behavioral;

add_mod_m_CG.vhdl

library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity adder_mod_m_CG is

port (

x, y: in std_logic_vector(3 downto 0);

addb_sub: in std_logic;

z: out std_logic_vector(3 downto 0)

);

end adder_mod_m_CG;

architecture rtl of adder_mod_m_CG is

constant M: std_logic_vector(3 downto 0) := conv_std_logic_vector(7, 4);

signal long_x, xor_y, sum1, long_z1, xor_m, sum2: std_logic_vector(4 downto 0);

signal c1, c2, sel: std_logic;

signal z1, z2: std_logic_vector(3 downto 0);

begin

long_x <= ‘0’ & x;

xor_gates1: for i in 0 to 3 generate

xor_y(i) <= y(i) xor addb_sub;

end generate;

xor_y(4) <= ‘0’;

sum1 <= addb_sub + long_x + xor_y;

c1 <= sum1(4);

z1 <= sum1(3 downto 0);

long_z1 <= ‘0’ & z1;

xor_gates2: for i in 0 to 3 generate

xor_m(i) <= m(i) xor not(addb_sub);

end generate;

xor_m(4) <= ‘0’;

sum2 <= not(addb_sub) + long_z1 + xor_m;

c2 <= sum2(4);

z2 <= sum2(3 downto 0);

sel <= (not(addb_sub) and (c1 or c2)) or (addb_sub and not(c1));

with sel select z <= z1 when ‘0’, z2 when others;

end rtl;

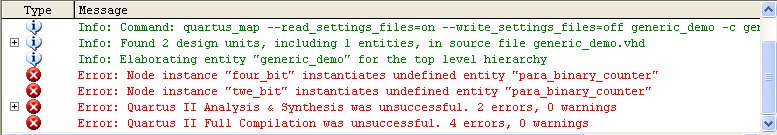

Reply